Partielle HDI-Technik im HDI pool

Partielle HDI-Technologie im HDI-Pool

Effiziente Lösungen für komplexe Designanforderungen

Immer mehr Elektronikdesigns enthalten einzelne Bauteile mit sehr feinen Anschlussrastern µBGAs, CSPs oder zweireihige QFNs. Diese Komponenten stammen aus mobilen Anwendungen und kommen zunehmend in IoT-fähigen und stromsparenden Systemen zum Einsatz.

Standard-Multilayertechnik stößt hier an Grenzen:

- Innenliegende Kontakte lassen sich nicht mehr sauber ausrouten.

- Stubs verschlechtern das Signalverhalten in High-Speed-Designs.

- Thermisch kritische Pads erfordern eine direkte Anbindung.

Eine vollständige HDI-Leiterplatte wäre technisch machbar, ist für Prototypen oder Kleinserien jedoch oft zu zeit- und kostenintensiv.

Die Alternative: Partielle HDI-Technik im Eurocircuits HDI pool.

Partielles HDI ist ideal, wenn nur wenige Bauteile mit feinem Pitch sicher in ein Design integriert werden sollen. Eurocircuits kombiniert dafür gezielte Microvia-Technologie mit standardisierten Multilayer-Prozessen und wirtschaftlicher Pool-Fertigung.

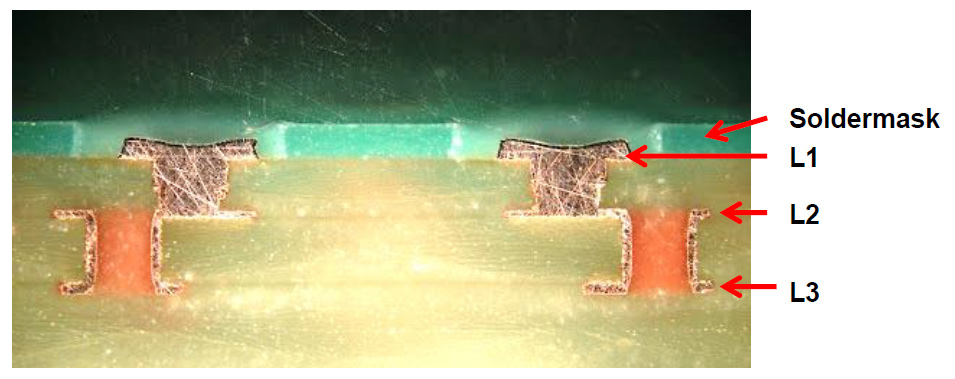

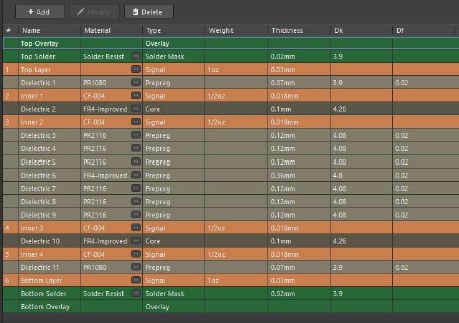

Im HDI pool stehen vordefinierte 6- oder 8-Lagen Multilayer mit 2 Microvia-Lagen auf einer Leiterplattenseite (partiell) zur Verfügung. Es werden staggered Microvias mit 100 µm Bohrdurchmesser verwendet, die zwischen L1-L2 gelasert und zwischen L2-L3 mechanisch gebohrt sind. Die Microvias zwischen L1-L2 sind sind galvanisch mit Kupfer verfüllt. Dadurch ist Via-in-Pad standardmäßig möglich ohne Voids oder Lötprobleme und ein sicheres, platzsparendes Routing auch bei 0,4 mm Pitch. Im Vergleich zu einem Full-HDI-Multilayer, ist die Konstruktion einfacher, schneller und kostengünstiger zu fertigen.

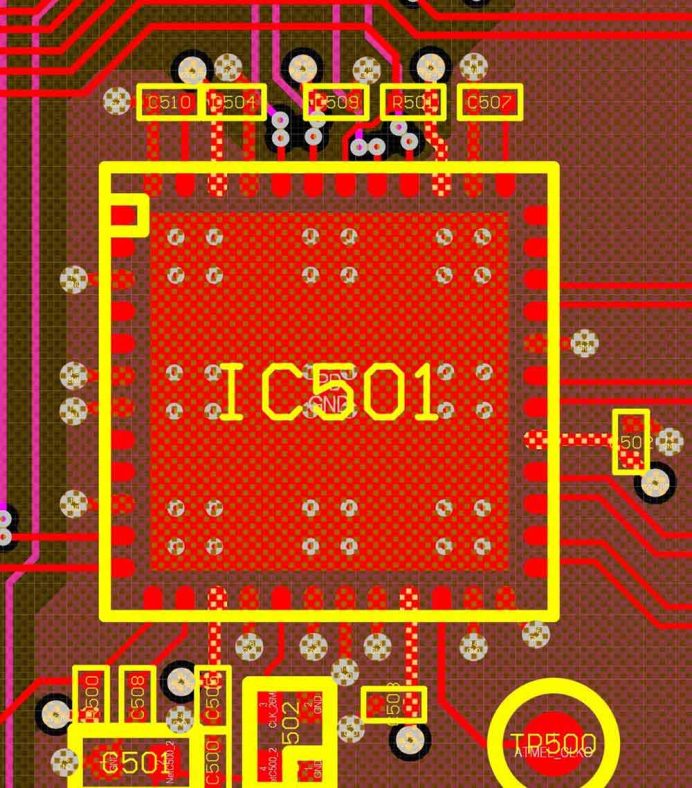

Wie Leiterplattendesigner mit dem HDI pool MicroBGAs präzise routen, High-Speed-Signale stubfrei führen und QFNs thermisch optimal anbinden, zeigen die HDI-Design-Profis von CIBOARD electronic an einem praxisnahen 6-lagigen Demoboard.

🟠 Beispiel 1: BGA-Integration mit 0,5 mm Pitch

Beispiel: Routing eines µBGA16 (4×4 Pins) mit 0,5 mm Pitch

- Hohe Pinnutzung

- Signalrouting über L1 und L3

- Referenzlage L2 (GND)

- GND-Anbindung über Microvias (L1/L2)

➡️ Vorteil: Kompakte, EMV-günstige Leiterbilder mit stabilen Bezugsebenen – ohne vollständigen HDI-Aufbau.

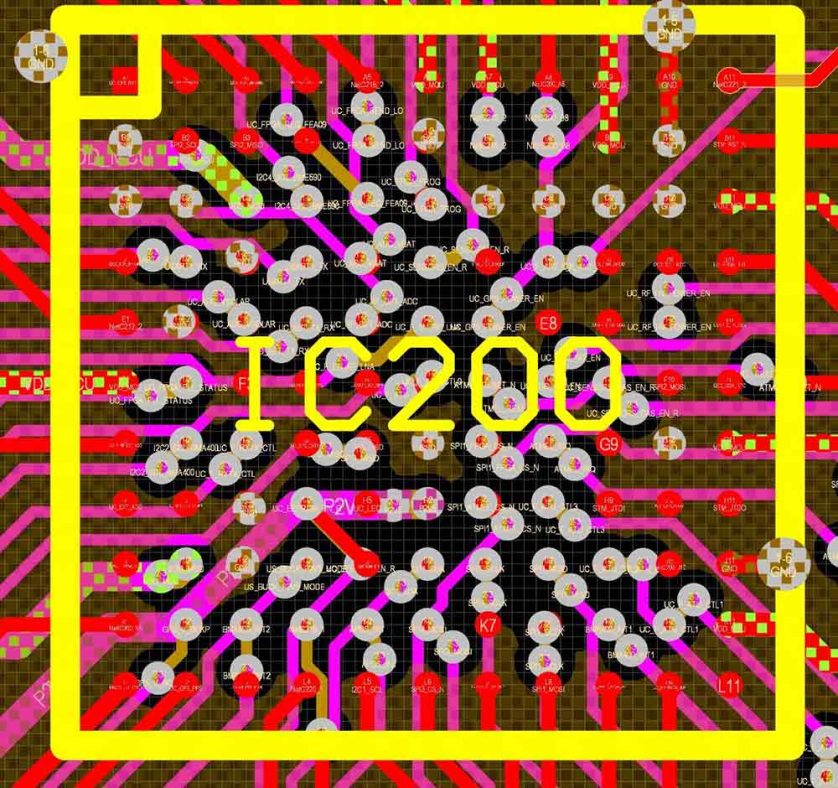

🟡 Beispiel 2: High-Speed-Designs und Impedanzkontrolle

Partielle HDI-Technik ermöglicht es, Differenzialpaare stubfrei zu routen und dadurch Signalqualität und EMV-Verhalten deutlich zu verbessern.

Beispiel: µBGA81 (11×11 Pins) mit 0,4 mm Pitch

- Mittlere Pin-Nutzung

- High-Speed differenzielle Leiterpaare

- Direkte L1–L3-Führung mit L2 als Referenzlage (GND)

Via-Stubs werden vermieden, Reflexionen reduziert und Impedanzen sauber kontrolliert.

💡 Profitipp: Referenzlagen konsistent halten, unnötige Lagenwechsel vermeiden und stubfreie L1–L3-Führung bei High-Speed-Signalen einplanen.

➡️ Vorteil: Verbesserte Signalintegrität und zuverlässiger Betrieb bei hohen Datenraten – ohne den Aufwand eines vollwertigen HDI-Designs.

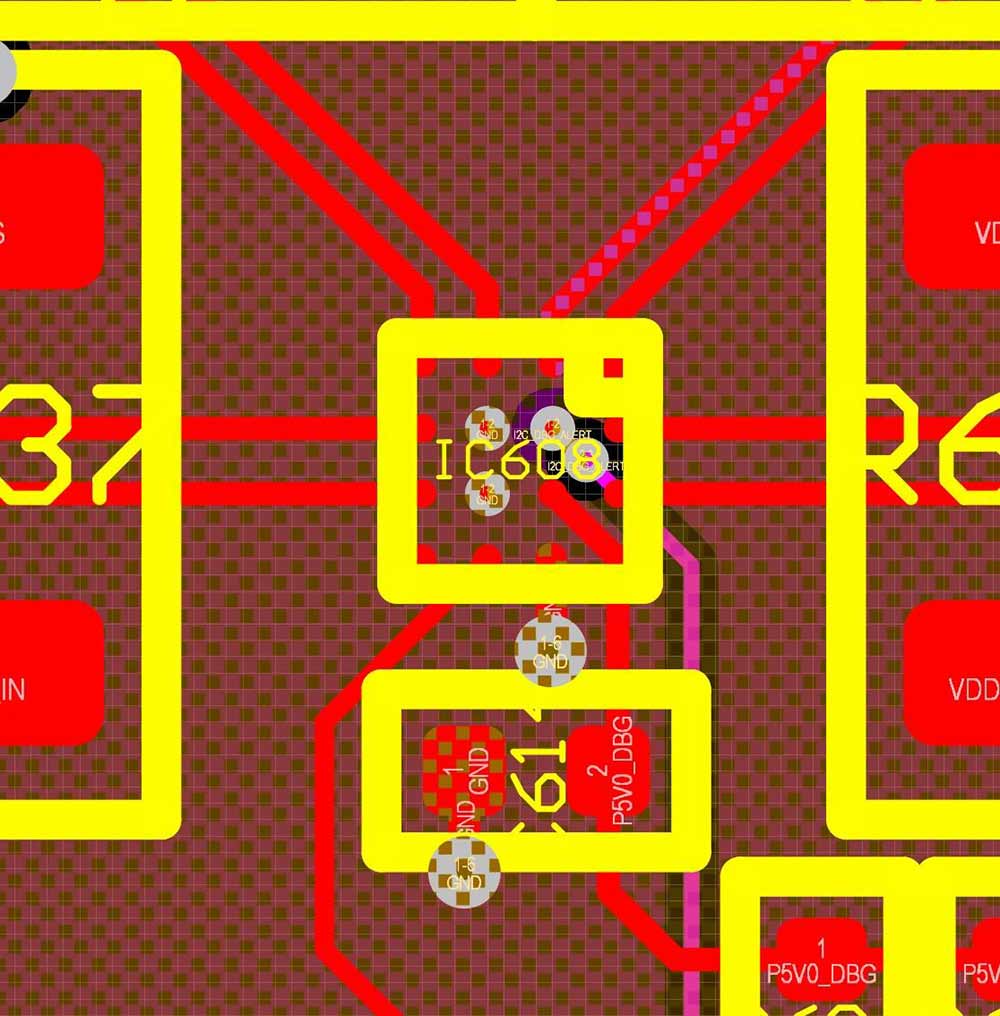

🔵 Beispiel 3: Thermische Anbindung von QFNs

Auch thermisch kritische Pads profitieren von der partiellen HDI-Technik.

Beispiel: QFN48 mit 0,5 mm Pitch

- Das Thermal Pad wird über Kupfergefüllte Microvias direkt an die GND-Referenzlage (L2) angebunden.

- Zusätzliche Microvias zwischen L2 und L3 verbessern die Wärmeverteilung weiter.

- Da die Microvias plan verfüllt sind, entstehen keine Lötprobleme wie bei offenen TH-Vias im Pad.

💡 Profitipp: Thermal Vias gezielt im Pad-Bereich platzieren, um Wärme zuverlässig in die Innenlagen abzuleiten und gleichzeitig die Lötqualität zu sichern.

➡️ Vorteil: Effizientes thermisches Management, höhere Zuverlässigkeit und längere Lebensdauer für leistungstragende Bauteile.

💻 EDA-Integration & wirtschaftliche Fertigung

Im HDI pool stehen vordefinierte 6- und 8-Lagen-Multilayer, Altium Designer Templates und ein Impedanzkalkulator im Visualizer zur Verfügung. Mit den Altium-Regeln können Leiterplattendesigner das Routing direkt im CAD mit den korrekten Parametern umsetzen und ihre Daten anschließend in den Eurocircuits Visualizer hochladen. Der Visualizer prüft die Daten automatisch (DRC/DFM), liefert sofort Preis und Lieferzeit und stellt sicher, dass das Layout vollständig poolfähig ist.

👉 Probieren Sie es aus: Laden Sie Ihr Design in den Eurocircuits Visualizer, prüfen Sie es online auf Fertigbarkeit und starten Sie direkt mit Ihrer partiellen HDI-Leiterplatte.

Vielen Dank an das Team von CIBOARD electronic für die Beispiele, Grafiken und Designtipps.

Webinar Partielles HDI in Aktion

Wir laden Sie zu einem kostenlosen Webinar ein. Anhand praxisnaher Beispiele zeigen wir mit den Profis von CIBOARD electronic, wie sich anspruchsvolle Gehäusetypen mit Microvias im Eurocircuits HDI pool sicher und effizient entflechten lassen – ohne den gesamten Lagenaufbau auf HDI umstellen zu müssen.

Wir demonstrieren, wie Sie die Altium-Designvorlagen optimal einsetzen und Ihr Layout anschließend mit dem Visualizer online prüfen können.

Anmelden zum Webinar „Partielles HDI in Aktion“