Partial HDI in Practice: FPGA High-Speed Routing Designer Insight

Designer Insights #1 Reale Projekte. Reale Herausforderungen. Reale Entscheidungen.

Was braucht es, damit ein High-Speed-FPGA-Design auf Anhieb funktioniert bei minimalem Bauraum und ohne unnötige Komplexität?

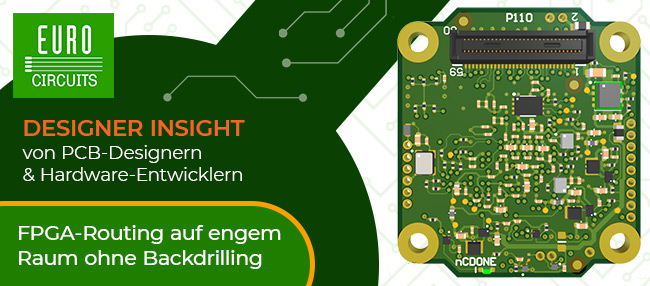

In unserem ersten Designer Insight zeigt Frank, CID+ (Certified Interconnect Designer) wie er ein dichtes Videosignal-Layout umgesetzt hat: begrenzter Platz, hohe Anforderungen an die Signalintegrität, Backdrilling keine Option.

Statt direkt auf Full HDI zu setzen, wählte er einen gezielten Ansatz: Partial HDI umgesetzt auf dem 8-Lagen-Aufbau im Eurocircuits HDI-Pool.

Durch saubere Lagenwechsel unter gemeinsamer Referenzfläche und den gezielten Einsatz von Microvias entstand zusätzlicher Routing-Spielraum bei gleichzeitig kontrollierter Komplexität.

Ein entscheidender Moment: Im PCB/PCBA Visualizer wurden Abweichungen bei BGA-Padgrößen früh erkannt und korrigiert, noch bevor sie Probleme verursachen konnten.

Ergebnis: ein schneller, kosteneffizienter Prototyp, der auf Anhieb funktioniert hat.

Ihre Arbeit interessiert uns

Das ist der Start unserer Serie Designer Insights mit echten Herausforderungen und praxisnahen Entscheidungen aus dem Alltag der Leiterplattendesigner.

Haben Sie eine ähnliche Aufgabe gelöst? Teilen Sie Ihre Erkenntnisse unserer Community anonym oder gern mit Nennung Ihres Unternehmens.

Bekanntlich entstehen ja die besten Lösungen, wenn man Wissen teilt.

Ihr

Uwe Dörr und das Eurocircuits Team