Entwickeln für HDI-Pool

Geschrieben von: Saar Drimer. 08/11/2024

Eurocircuits HDI Pool ermöglicht Microvias zwischen den Lagen L1-L2 und L2-L3 (oder alternativ L6-L7 und L7-L8). Weil die Leiterplatte mit unseren Parametern für die Standardleiterplattentechnik gefertigt wird, zwei Microvia-Lagen und HDI- Merkmale (High Density Interconnection) nur auf einem Teil der Leiterplatte hat, ist unsere Lösung, die auch partielles HDI genannt wird, preisgünstiger als eine volle HDI-Leiterplatte. Wenn wir also ein einzelnes Fine-Pitch-BGA verwenden wollen oder müssen, weil es keine Alternative gibt, muss das nicht unbedingt eine sehr teure Leiterplatte bedeuten.

Dieser Beitrag zeigt die Möglichkeiten, wie man das Potenzial des HDI Pools optimal nutzen kann.

Der Einstieg

Es ist schwer zu sagen, ob man einen BGA entflechten kann und wie viele Lagen es dafür braucht, bevor man es versucht. Es gibt eine Vielzahl von Faktoren, die es möglich oder unmöglich machen: die Leiterplattentechnologie und die Beschränkungen bei der Bestückung, die Anzahl der verfügbaren Routing-Lagen, die Anzahl der BGA-Anschlüsse (nicht alle BGAs mit voll mit Pins), die Anordnung der Pins (eine Gruppe von Stromversorgungspins ist hilfreich), die Anzahl der vom Design verwendeten Anschlüsse (bei vielen Designs werden z. B. nicht alle Pins eines Mikrocontrollers verwendet) und die Platzierung der übrigen Bauteile im Verhältnis zur Pin-Belegung des BGA (wenn sich z. B. ein Speicherbus über das gesamte Array erstreckt, wird das Routing schwieriger).

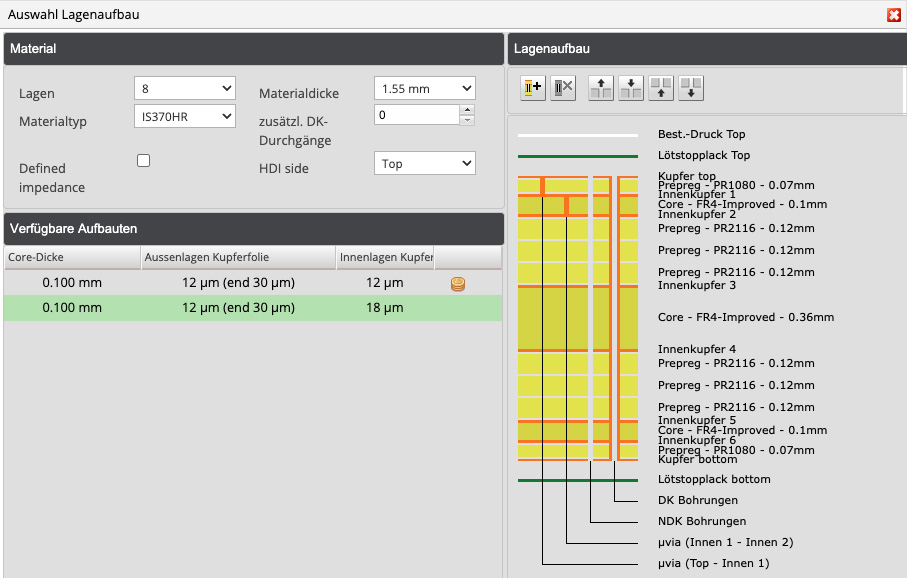

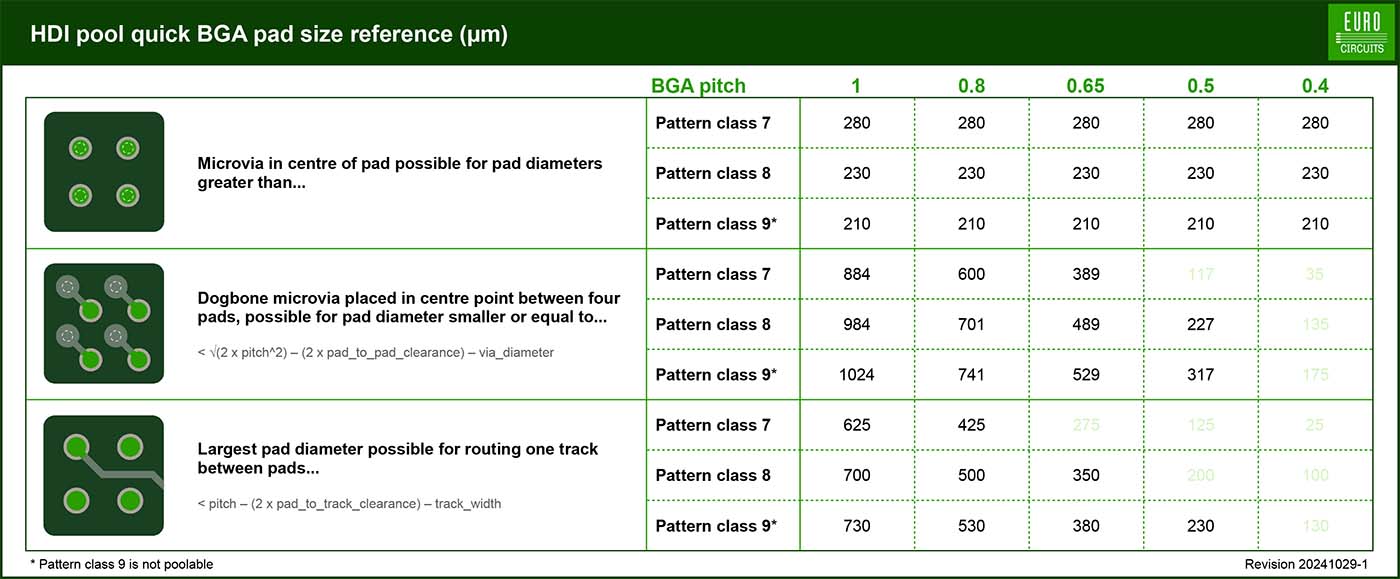

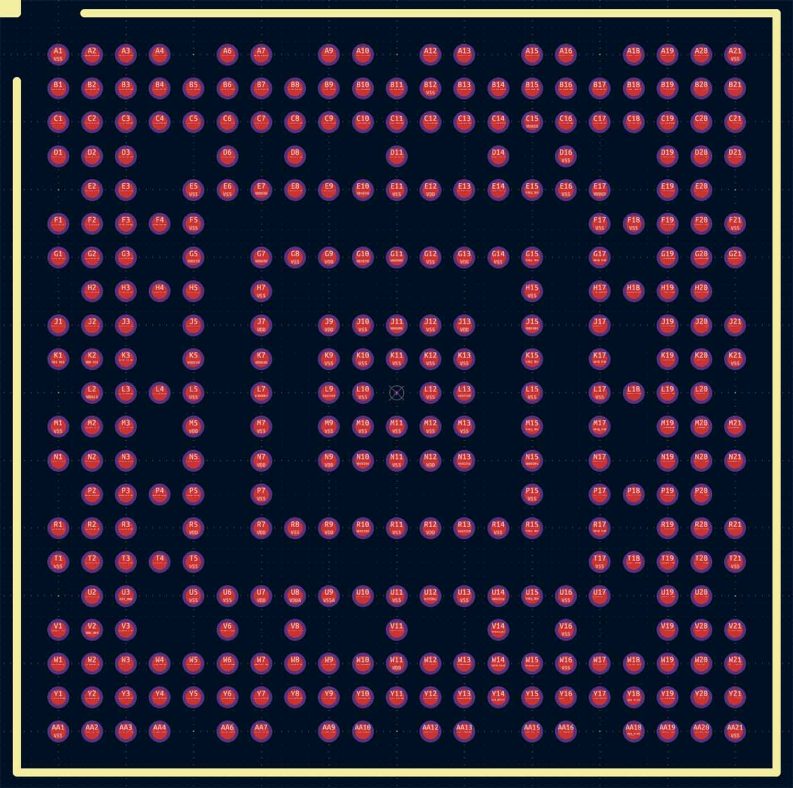

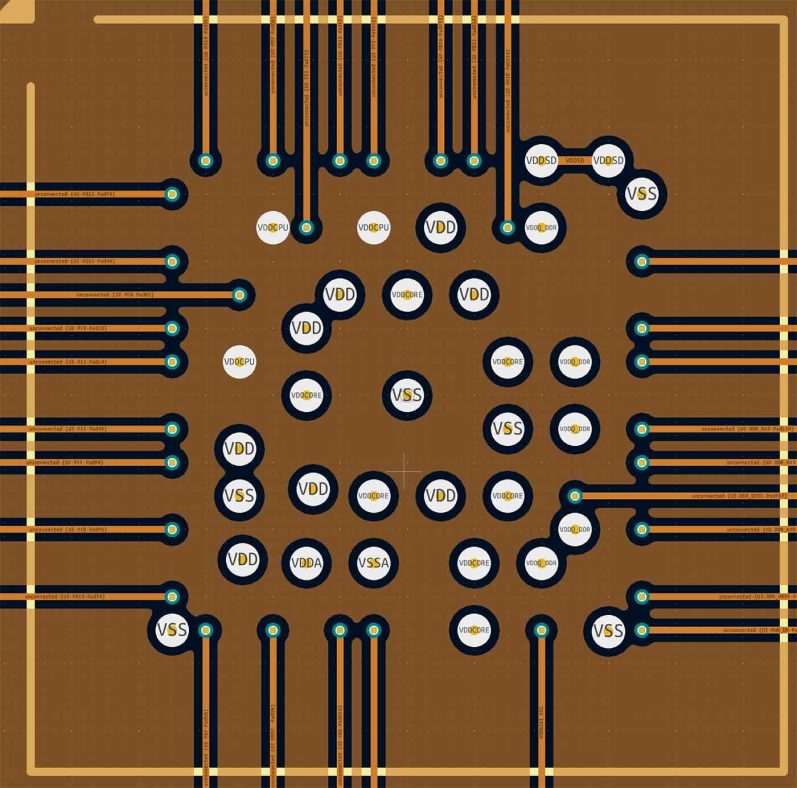

Für die Leiterplattenfertigung und die Bauteilebestückung haben wir die beiden bereits erwähnten HDI-Microvia-Läufe und unsere Musterklassen, die Leiterbahnbreiten, -abstände, Pad- und Lochdurchmesser usw. Festlegen. Diese Parameter sind in Bild 1 dargestellt. Wir unterstützen nur versetzt angeordnete (staggered) Microvias, bei denen sich die Bohrungen nicht überlappen. Der Mindestabstand muss 0.010 mm (10 µm) betragen. (Das bedeutet im Umkehrschluss, dass wir keine gestapelten (stacked) Vias unterstützen). Die Anzahl der Lagen ist einfach: Der HDI Pool hat nur den in Bild 2 dargestellten 8-Lagen-Pool-Aufbau. In Zukunft können weitere hinzukommen. Die anderen Aspekte, die bestimmen, ob eine Schaltung routingfähig ist oder nicht, sind designabhängig und liegen natürlich außerhalb der Kontrolle des Leiterplattenherstellers.

Wir werden uns nun auf Layouts konzentrieren, die das Entflechten eines BGA im Allgemeinen und im Besonderen mit dem HDI Pool unterstützen können.

Nützliche Tipps

Ein guter Ausgangspunkt zum Entflechten eines BGAs ist die Frage, ob wir ein Microvia Pad-Mitte platzieren können. In der Praxis bedeutet das, dass der vom Bauteilehersteller angegebene Durchmesser des Kupferpads gleich oder größer sein muss als der Durchmesser des Microvia-Pads in der Leiterbildklasse – manchmal auch als Restring bezeichnet.

Das ist in der ersten Zeile von Bild 3 dargestellt. Hier ist einfach die Mindestgröße der Microvia-Pads für jede Leiterbildklasse aufgeführt. Wenn die Pad-Größen des BGA etwas kleiner als das Microvia-Pad sind, liegt es im Ermessen des Leiterplattendesigners, sie zu vergrößern. Normalerweise gibt es eine gewisse Flexibilität für den genauen Wert, wobei einige Hersteller nur einen Bereich oder gar keinen Wert angeben.

Es ist ebenfalls sinnvoll, frühzeitig zu wissen, ob ein Dog-Bone-Routing (Vias neben das BGA-Pad gesetzt) und Leiterbahnen zwischen den Pads möglich sind. Die zweite und dritte Zeile in Bild 3 zeigen die größten BGA-Pad-Durchmesser, mit denen dies möglich ist.

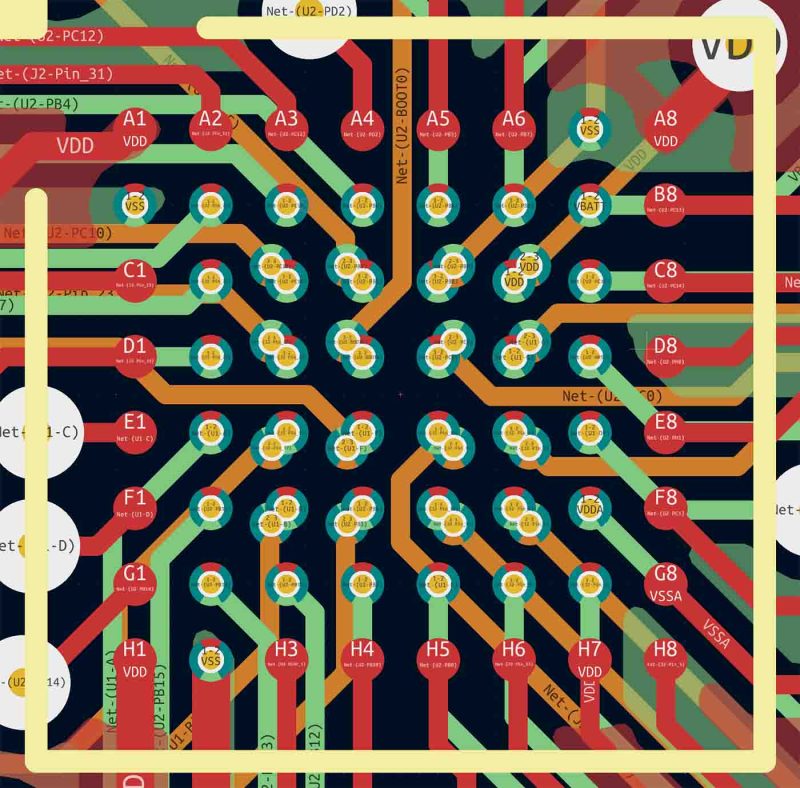

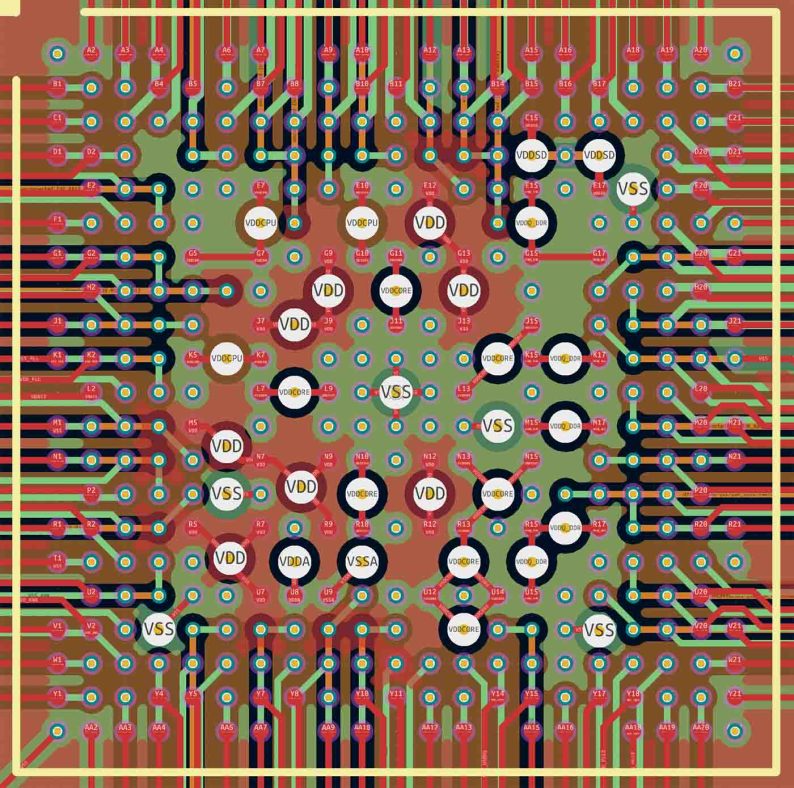

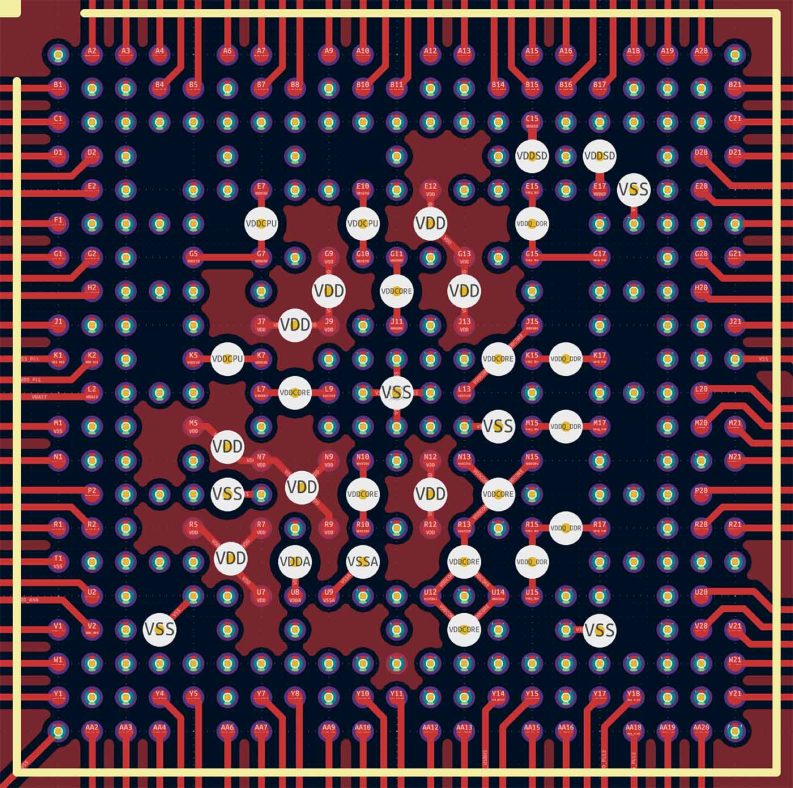

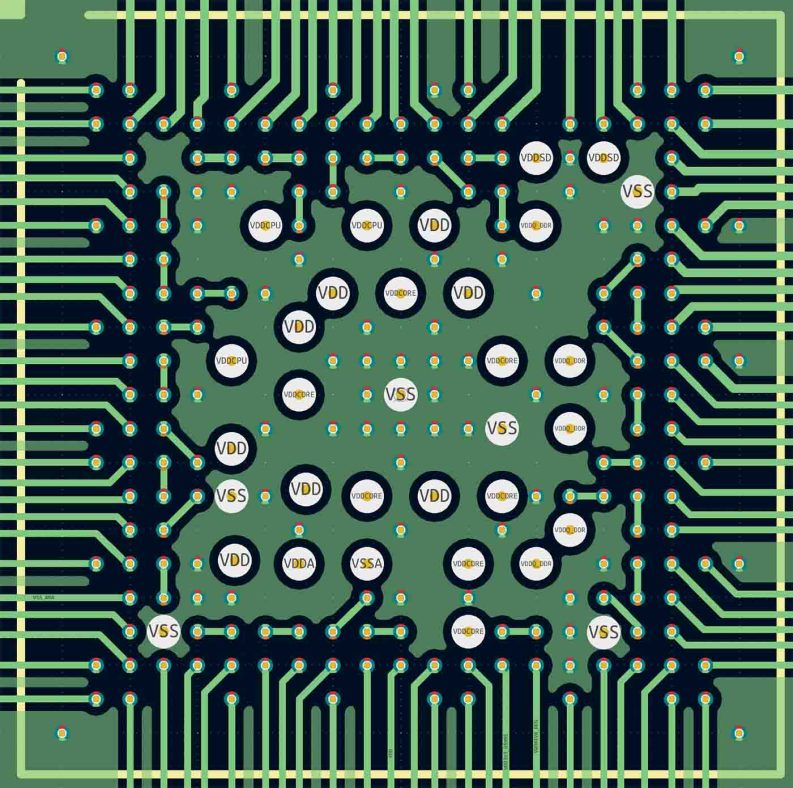

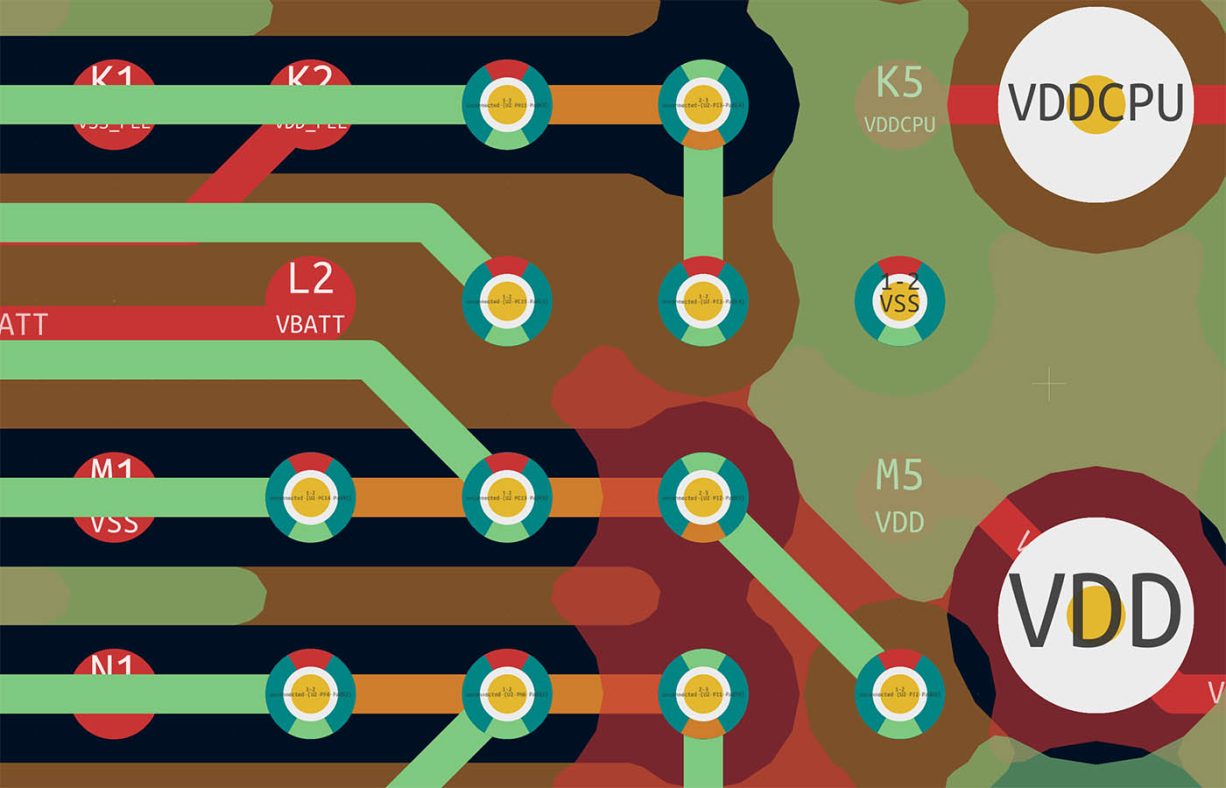

Schauen wir uns nun ein 8×8 BGA-Array an. Eine grundlegende Entflechtungsstrategie ist, die Array- „Reihen“ des BGAs von außen nach innen zu betrachten. Die erste Reihe wird in Lage L1 geroutet und die zweite Reihe in L2 mit L1-L2-Microvias. Die dritte und vierte Reihe können in L3 geroutet werden, wobei versetzt angeordnete (staggered) Microvias L1-L2 und L2-L3 verwendet werden. Ein Beispiel für ein vollständig geroutetes 8×8 BGA zeigt Bild 4. Hier wurde unsere Leiterbildklasse 8 (mit Bohrklasse E für die Durchkontaktierungen) verwendet.

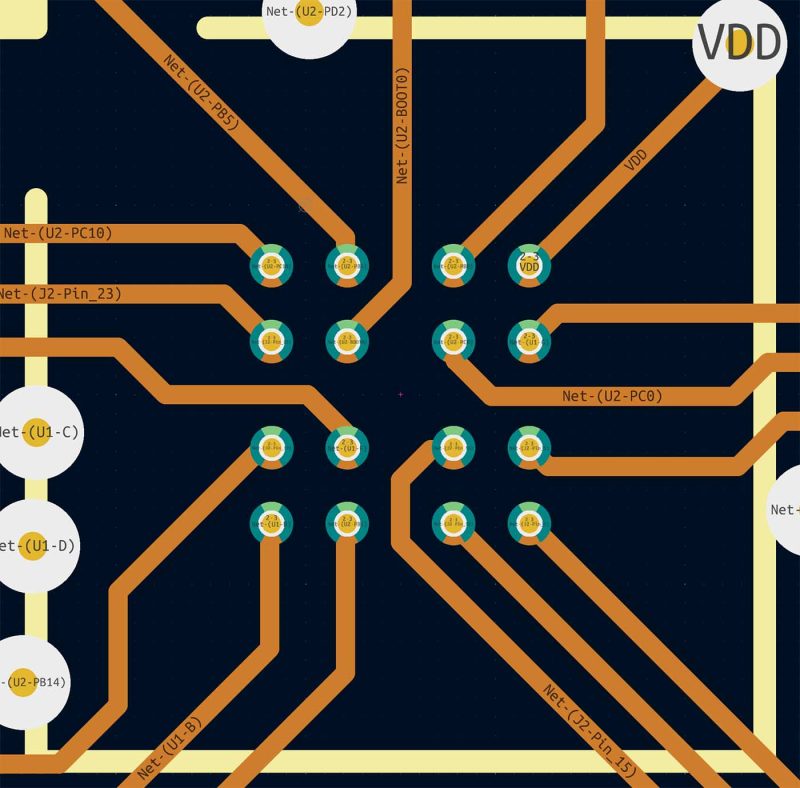

Aus dieser Strategie können wir noch einige weitere Dinge lernen. Die Microvias L1-L2 befinden sich in der Pad-Mitte. Sie haben zufällig genau den gleichen Durchmesser und die versetzt angeordneten Microvias L2-L3 sind symmetrisch nach Quadranten ausbalanciert. Das hilft uns, die innersten Reihe zwischen diesen Microvias zu entflechten (siehe Bild 5). Diese Anordnung ist auch für die Leiterplattenbestückung sehr hilfreich, weil sich die Wärme gleichmäßig über die BGA-Pins verteilt. Damit sinkt die Wahrscheinlichkeit, dass sich das BGA im Lötprozess verschiebt und nicht mehr korrekt ausgerichtet ist.

Mit der Begrenzung auf zwei Microvia-Lagen ist diese Strategie nicht unbedingt geeignet, um alle Pins eines vollständigen BGAs mit mehr als 8×8 oder 9×9 Anschlüssen zu entflechten. Es gibt jedoch mehrere Faktoren, die das auch für viel größere Arrays ermöglichen. Betrachten wir dazu ein BGA mit 320 Anschlüssen und 0,5 mm Ball-Pitch, dargestellt in Bild 6, und sein Fan-out in Bild 7.

Wie zuvor werden die äußersten Anschlüsse des BGA auf L1 geroutet (Bild 7), wobei die Platzierung der Stromversorgungs- und Masse-Pins sowie der Pin-Lücken mit Hilfe von Durchkontaktierungen (0,5-mm-Pads mit 0,15-mm-Bohrung, also Bohrklasse D) hilfreich ist. Das Routing der nächsten Reihe ist in Bild 8 dargestellt, zusammen mit dem Routing zwischen den Microvias L1-L2 und L2-L3, wobei letztere auch in den Pin-Lücken platziert sind (Bild 9). Die restlichen Signalpfade werden in L3 verlegt (Bild 10).

Wie zuvor platzieren wir die Anschlüsse der äußeren Reihe auf L1 (Bild 8). Stromversorgungs- und Masse-Pins befinden sich in den Pin-Lücken mit Durchkontaktierungen (0,5 mm Pads mit 0,15 mm Durchmesser, also Bohrklasse D). Die Leitungsführung der nächsten Reihe ist in Bild 9 zusammen mit dem Routing zwischen den Microvia-Lagen L1-L2- und L2-L3 dargestellt, wobei letztere auch in den Pin-Lücken platziert sind (Bild 10). Die restlichen Signalpfade werden schließlich in Lage L3 platziert (Bild 11).

Es ist wichtig zu erwähnen, dass in unseren Beispielen alle BGA-Anschlüsse nach außen geführt wurden. Viele Designs verwenden nicht alle Pins des BGAs. Das kann das Entflechten vereinfachen. Die Parameter des HDI Pools sind so gewählt, dass wir die meisten 8×8-BGA-Gehäuse vollständig entflechten können. Wir sind zuversichtlich, dass auch größere Arrays in realen Designs funktionieren.

Wie geht’s weiter?

Eurocircuits Visualizer mit dem HDI Pool vertraut zu machen. Dann sollten Sie ein Design hochladen, um zu testen, wie effektiv der HDI Pool beitragen kann, die Kosten für ein Leiterplattendesign mit einem BGA zu senken.