CAM-CAD Kommunikation: Der Schlüssel für ein besseres Leiterplattendesign

Dass es für eine reibungslose Zusammenarbeit wichtig ist, dieselbe Sprache zu sprechen, liegt auf der Hand – gerade bei technischen Daten für die Fertigung. Leiterplattendaten werden mit CAD-Software (Computer-Aided Design) erstellt und anschließend an den Hersteller übermittelt, der sie mithilfe von CAM-Software (Computer-Aided Manufacturing) für die Produktion aufbereitet. (CAD ist ein Oberbegriff, der auch EDA – Electronics Design Automation – umfasst; hier verwenden wir die Begriffe synonym.)

Wie die Begriffe bereits andeuten, eignet sich CAD hervorragend für das Designen von Leiterplatten, hat aber Schwächen in der Analyse (etwa DRC = Design Rule Check und DFM = Design for Manufacturing). CAM ist das Gegenstück: Es ist stark in der Analyse, aber nur eingeschränkt in der eigentlichen Gestaltung und berücksichtigt dabei meist auch nicht die elektrische Funktion (die oft nur als Schaltplan vorliegt und selten mit den Daten übermittelt wird). Anders gesagt: Ein Designer kann eine funktionierende Leiterplatte vom Hersteller zurückbekommen, ohne viel über den Herstellungsprozess selbst zu wissen.

Leiterplatten werden oft produziert, ohne dass Designer und Hersteller je direkt miteinander sprechen. Das liegt nicht daran, dass die Daten (Gerber, ODB++ etc.) perfekt wären, sondern daran, dass die CAM-Seite gelernt hat, die Absichten der Designer zu erraten. Diese Praxis ist eine Art Überlebensstrategie, um mit unvollständigen oder fehlerhaften Spezifikationen, Software-Bugs oder einer sehr unterschiedlichen Datenqualität umzugehen. Dieses „Raten“ ist auch nötig, weil – wie bereits erwähnt – viele Designer mit den Details der Fertigung nicht vertraut sind. Deshalb können auch Fehler entstehen.

Gute Leiterplattenhersteller versuchen, dieses Rätselraten zu minimieren, indem sie dem Leiterplattendesigner Rückmeldungen (Daten-Feedback) geben: Sie stellen Fragen zu den Daten und machen Vorschläge zur Korrektur. Das geschieht bewusst sparsam, um Verzögerungen zu vermeiden und den Designer nicht zu verärgern. Der Vorteil liegt jedoch auf der Hand: Der PVB-Designer kann Fehler an seinem Design korrigieren, damit sie bei zukünftigen Aufträgen gar nicht erst auftreten. Dennoch: Obwohl die Daten im Wesentlichen identisch sind, sehen CAD und CAM die Welt unterschiedlich – und sprechen auch eine andere Sprache.

Ein paar typische Unterschiede

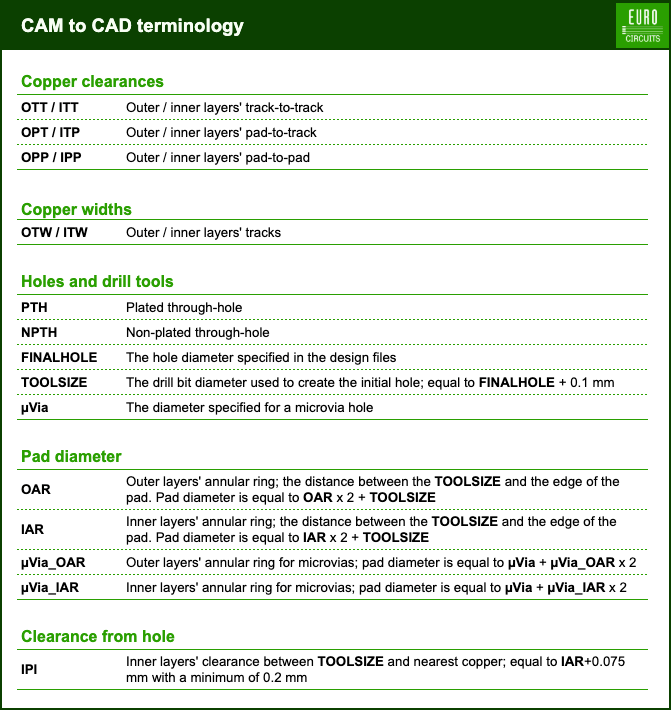

PCB-Designer konzentrieren sich oft auf nur einen Mindestabstand: den Abstand zwischen Kupferflächen unterschiedlicher Netze. Dieses Maß gilt für jede Kupferstruktur – egal ob Leiterbahn, Pad oder Kupferfläche. Hersteller dagegen unterscheiden hier in viele Clearance-Arten, die ihre CAM-Software wiederum einzeln analysiert. Abbildung 1 zeigt die verschiedenen Clearance-Kategorien bei Eurocircuits: Zuerst wird zwischen Außen- und Innenlagen unterschieden, dann folgt die Aufteilung nach Kupferstrukturen. Das ist wichtig, weil Hersteller jede dieser Kategorien unterschiedlich behandeln können: Für manche können sie kleinere Anpassungen machen, damit das Design die Prüfungen besteht, für andere geht das nicht oder ist nur eingeschränkt möglich – abhängig von ihren Prozessen und ihrem Know-how.

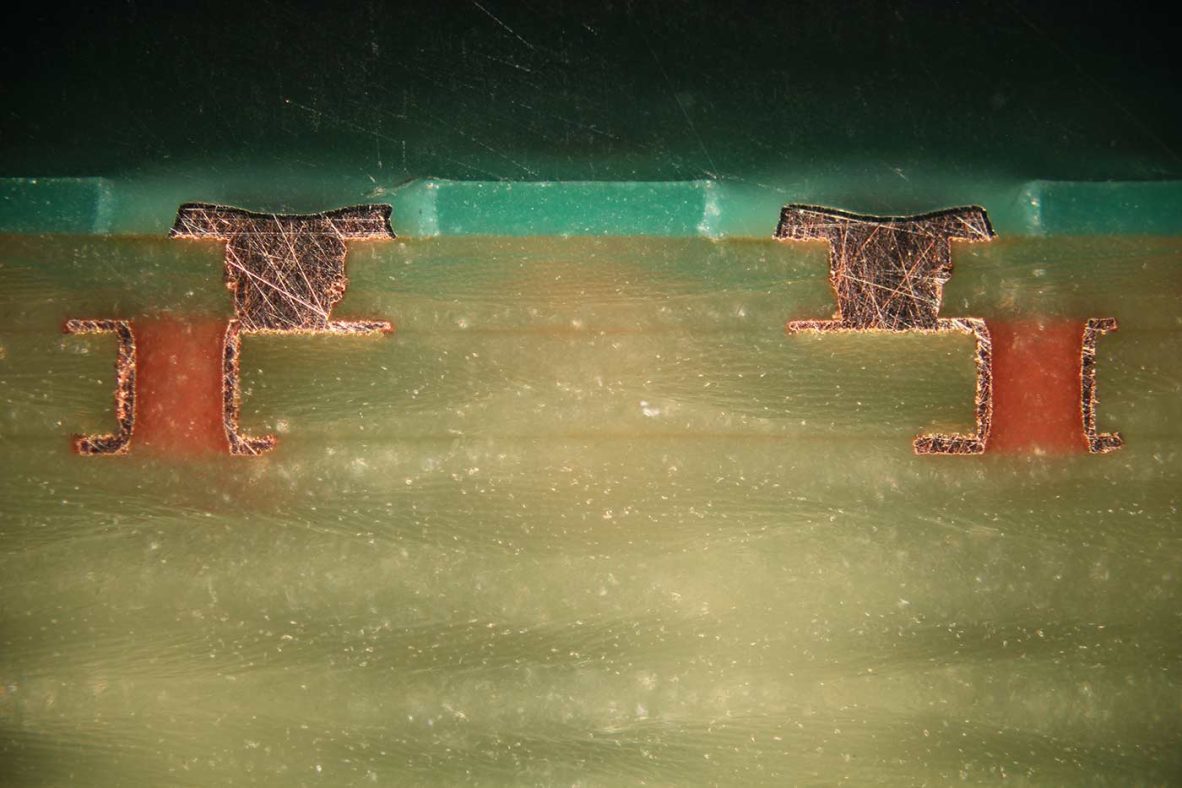

Bei runden Pads interessiert sich der Designer meist für den kleinsten technologisch möglichen Durchmesser. Das ist wichtig, um schnell beurteilen zu können, ob Vias noch passen oder ob eine Leiterbahn zwischen Pads passt. Aus CAM-Sicht ist das aber deutlich komplexer: Eine Durchkontaktierung im Pad herzustellen, ist nicht so einfach wie die Definition in den Daten!!

Im CAD spricht man meist vom Pad-Durchmesser, während CAM lieber mit dem Begriff Restring arbeitet – das ist der Pad-Durchmesser minus der Lochdurchmesser geteilt durch zwei. Wie wandelt man das um? Damit eine leitfähige Bohrung (Via) gefertigt werden kann, muss der Hersteller ein etwas größeres Loch bohren, um die Kupferschicht der Bohrung zu berücksichtigen. Hier kommt TOOLSIZE ins Spiel: Er entspricht dem FINALSIZE (also dem definierten Lochdurchmesser im Design) plus 0,1 mm (für die Kupferplattierung). Um den kleinsten Pad-Durchmesser zu ermitteln, muss man also den TOOLSIZE plus zweimal den Restring addieren (nicht den FINALSIZE!). (Bei nicht durchkontaktierten Bohrungen ist es einfacher: TOOLSIZE und FINALSIZE sind gleich.)

Bei Microvias wird es noch komplexer: Manche sind mit Kupfer gefüllt (z. B. in unserem (z. B. in unserem HDI-Pool L1-L2-Vias), andere werden gebohrt, metallisiert und mit Harz gefüllt (L2-L3-Vias). Hier gibt es keinen TOOLSIZE-Wert, um den Pad-Durchmesser aus dem Restring zu berechnen – und manchmal bleibt auf der Leiterplatte überhaupt keine Bohrung, obwohl eine in den Daten definiert ist! Das ist ein weiteres Beispiel dafür, dass Realitäten in der Fertigung für den PCB-Designer oft unsichtbar bleiben.

Wie gelingt ein besseres Leiterplattendesign?

Je besser wir als Leiterplattendesigner die Details des Fertigungsprozesses verstehen, desto mehr fließt dieses Wissen in unsere Denkweise und unsere Arbeitsabläufe ein. Das Resultat: besseres DFM, schnellere Freigaben und weniger Kosten. Der erste Schritt dahin ist, die Sprache der Hersteller zu lernen – um ihre Richtlinien und ihr Feedback besser zu verstehen. Diese Kluft zu überbrücken kostet zwar etwas Mühe, zahlt sich aber aus.